I. Introducción

Los sistemas de estaciones base de telefonía celular 4G y 5G requieren amplificadores de microondas con alta potencia de salida, baja distorsión y alta eficiencia. Uno de los desafíos en su implementación es reducir al máximo posible el área de diseño del circuito impreso (PCB), lo cual es fundamental para mantener el costo del amplificador a un mínimo [1]. Las tecnologías RFIC proporcionan, en este sentido, soluciones rentables, confiables y competitivas para estos desafíos. Por otro lado, desde el punto de vista de los semiconductores, LDMOS es una de las tecnologías actualmente en uso, pero aún bajo investigación. Esta tecnología tiene una densidad de potencia mejorada en comparación con los semiconductores de compuestos tradicionales [1]. Sin embargo, LDMOS presenta problemas con la disipación de energía, lo cual crea fenómenos de dispersión de frecuencia, conocidos como efectos trampa (trapping) y efectos térmicos [2].

Se han propuesto varias técnicas para reducir los problemas térmicos. Una de ellas es la técnica de seguimiento térmico (“thermal-tracking”) [3], que consiste en la inclusión de una red de retroalimentación para que el dispositivo sea robusto contra los cambios de temperatura. Aunque se mejoraron algunos problemas térmicos, siempre hay variaciones en el rendimiento, no solo debido al efecto de calentamiento, sino también debido a la variación de frecuencia de la señal de entrada que crea efectos memoria [1].

Otra forma de enfrentar este desafío es usar modelos electrotérmicos realizados en herramientas CAD, con el objetivo de predecir las condiciones en las que aparecerán esos fenómenos. Con esa información, el ingeniero diseñador de RF puede, por ejemplo, evitar polarizar el transistor en esas condiciones antes de la implementación del amplificador de potencia final, ahorrando tiempo y dinero en la industria de los transistores de microondas. Una de estas técnicas es el modelo térmico mostrado en [4], el cual utiliza una red con una resistencia térmica y un capacitor térmico en el drenador del transistor intrínseco. Este método permite modelar a dispositivos LDMOS de hasta 10 A de corriente de drenador. Este modelo fue derivado usando medidas pulsadas.

Otra de estas técnicas se expone en [5], la cual usa como punto de partida las medidas pulsadas indicadas en el modelo anterior, pero extendidas a compuerta y drenador a través de la técnica de los voltajes efectivos. En dicho artículo, la técnica se usó para modelar dispositivos en tecnología GaAs. En este documento se demostrará que esta última técnica también se puede utilizar en dispositivos RFIC a 3,5 GHz.

Sin embargo, además de la elección de las condiciones óptimas para minimizar el autocalentamiento, es necesario determinar la cantidad de metalización y dimensiones geométricas óptimas del transistor que permitirán maximizar su comportamiento en términos de potencia, eficiencia y linealidad. Al ser un problema de optimización multidimensional, es necesario hacer una actividad exploratoria en varias dimensiones, denominada diseño de experimento (DOE). Los experimentos terminan cuando no sea posible obtener mejoras significativas variando los parámetros en todas sus dimensiones. En [6] y [7] se usó el método de Plackett-Burman para hacer un análisis de regresión lineal para evitar el uso de circuitos eléctricos equivalentes. En [6] se lograron ajustar cinco parámetros. En el presente estudio se lograron ajustar siete parámetros: cuatro de los cuales representan diferentes niveles de metalización del die; mientras que los otros tres representan diferentes alturas de los hilos de salida (output wire-bonds).

En este artículo se parte de la hipótesis de que mediante el uso de un Design of Experiment (DOE) extendido, en combinación con un modelo electrotérmico mejorado con la técnica de voltajes efectivos, se podrá construir eficientemente amplificadores de potencia de RF en el rango de microondas, para reducir tiempos de diseño y costos en el proceso de fabricación, y garantizar su funcionamiento en una zona segura, extendiendo su confiabilidad.

En la segunda sección, de materiales y metodología, se detalla la estructura interna del dispositivo bajo prueba RFIC. Se especifican sus etapas y la importancia de los wire-bonds de salida en la preadaptación de impedancias. En cuanto a la metodología, se expone la naturaleza multidimensional en la optimización del diseño tanto en la longitud geométrica de los wire-bonds como en la metalización. Con el fin de evitar simulaciones electromagnéticas de alto costo computacional, se desarrollan prototipos con diferentes alturas de hilos de salida y se procede a medir el desempeño del RFIC. El diseño de experimento es ampliado a siete variables y se detiene cuando no se obtienen mejoras adicionales en los parámetros de rendimientos medidos (potencia, ganancia y eficiencia).

En la tercera sección se detallan los resultados del DOE extendido, combinado con el modelo dinámico pulsado basado en los voltajes efectivos. Para ello se usan medidas de Source-Pull, a fin de identificar las impedancias óptimas de adaptación a la entrada. Posteriormente se usan medidas Load-Pull para identificar las impedancias óptimas de salida que generen el mejor compromiso en potencia, ganancia, eficiencia y linealidad. Habiendo calculado estos valores puntuales, se realiza una medida de barrido en potencia para ver el comportamiento global del dispositivo y verificar que el modelo propuesto pueda predecir todas estas medidas. Finalmente, en la última sección se desarrolla un circuito impreso donde se pone a prueba el RFIC y el modelo haciendo medidas de temperatura. Se puede demostrar que el autocalentamiento es mínimo y que la distribución de calor es óptima, lo cual permite validar el método propuesto y garantizar la vida útil del amplificador en su totalidad.

II. Materiales y Métodos

A. Materiales

El RFIC utilizado en este documento como vehículo de prueba para validar nuestra prueba de concepto es el MW7IC3825 diseñado y desarrollado con material de tecnología LDMOS [8]. En [9] se ha demostrado que es posible diseñar un amplificador de potencia en PCB con el mencionado RFIC. En el presente artículo se propone mejorar el proceso interno de fabricación de dicho transistor. El RFIC utilizado es un amplificador de potencia integrado de dos etapas: un preamplificador y un amplificador propiamente dicho. Para distribuir y disipar el calor de manera eficiente, la etapa final se dividió en cuatro bloques activos y el preamplificador en dos bloques activos. Teniendo en cuenta que las estaciones base requieren amplificadores con alta potencia, alta eficiencia y baja distorsión, la etapa del preamplificador fue diseñada para funcionar con la máxima eficiencia, mientras que la etapa amplificadora final fue diseñada para funcionar con el mejor compromiso entre eficiencia y potencia para optimizar la potencia DC de consumo.

B. Metodología

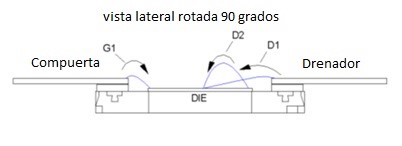

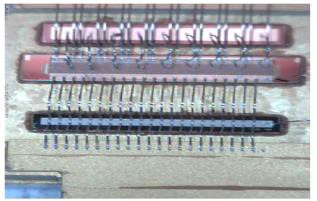

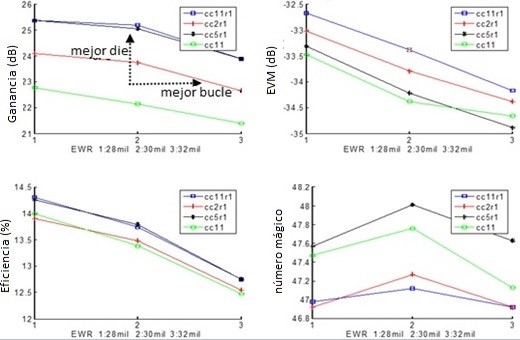

En frecuencias en el orden de los GHz y con potencia de varios Watts, deben considerarse los efectos de interferencia electromagnética de las inductancias mutuas de los wire-bonds. Para solucionar esto se realizó una prueba de diseño de experimento (DOE) extendido basado en [6] y [7], con el objetivo de probar el funcionamiento RF con diferentes alturas de bucle para los hilos de salida. En la Figura 1 se muestran las etiquetas G1, D2 y D1, que forman parte de la red de preadaptación, tanto en la puerta como en el lado del drenador. D2 y D1 representan el arreglo de wire-bonds en el lado del drenador, mientras que G1 representa el arreglo de wire-bonds en el lado de la compuerta. La Figura 2 muestra una foto de dicho RFIC sin encapsulado, donde se aprecia el die (transistor) en forma de bus-bar en la parte central de la imagen. Para la optimización de la altura de bucle D2, por ejemplo, se hicieron mediciones preliminares de ganancia, linealidad y eficiencia para tres valores diferentes de altura de bucle, con una señal estándar Wimax. El mismo procedimiento se utilizó para los demás hilos. La Figura 3 muestra los resultados para diferentes tipos de die, denotados por las etiquetas cc11r1 cc5r1 cc2r1 y cc11. La variación en el eje horizontal representa la altura del bucle D2; mientras que la variación en el eje vertical representa un tipo de die con diferente concentración de metalización.

En esa figura es posible ver que la versión de die denominada "cc5r1", con 2 mils de altura de bucle, muestra en general un mejor comportamiento en los tres parámetros más importantes de un amplificador: de ganancia, eficiencia y linealidad (EVM). Se ha tomado como unidad de medida de longitud al “mil”, equivalente a la milésima de una pulgada, debido a que es la unidad estándar usada en este tipo de procesos. El término de “número mágico” que se muestra en la parte inferior derecha de la figura es una constante definida por el diseñador de RF, que representa el mejor compromiso entre los parámetros indicados anteriormente, dado a través de una ponderación matemática entre ganancia, eficiencia y linealidad. La mejora más importante en el DOE presentado es que nos permite elegir tanto el die con mejor metalización, como la mejor dimensión de la altura de bucle D2. De esta manera, el diseñador puede asegurarse de que el diseño del RFIC esté centrado y obtenga su mejor desempeño, evaluando los efectos de la inductancia mutua sin necesidad de simulaciones electromagnéticas, que son de elevado costo computacional para este tipo de amplificadores, ahorrando tiempo en el proceso de diseño industrial.

III. Resultados

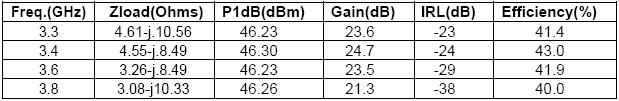

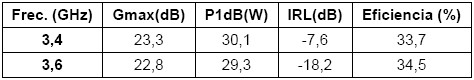

Una vez centrado el diseño, se realizaron medidas pulsadas directamente sobre el RFIC utilizando el sistema convencional de Load-Pull con sintonizadores pasivos [10]. El ancho de pulso fue de 9 µs con un ciclo de trabajo del 10 % para estudiar el comportamiento dinámico reduciendo los efectos de calentamiento al mínimo y manteniendo constante el punto de polarización de DC. Polarizando el dispositivo con 28 voltios en drenador, 70 mA de corriente de drenador para la primera etapa y 280 mA para la corriente de reposo para la segunda etapa, fue posible capturar la expansión de ganancia típica de esta tecnología [8]; y, en consecuencia, en este punto se midió la correcta potencia en condiciones de compresión 1dB. La Tabla 1 resume los resultados de las medidas mostrando una eficiencia de drenaje de las dos etapas del 40 % para la frecuencia más alta.

En el presente trabajo, para anticipar los resultados de las medidas durante la fase de diseño, se modificaron los modelos ROOT y MET electrotérmico [11] para el dispositivo de prueba antes señalado. La manera de modificarlos a través de la técnica de los voltajes efectivos fue mencionada en [9]. Sin embargo, en este trabajo se presenta una nueva función de la modificación antes mencionada, usando medidas del tipo “barrido en potencia” en diferentes frecuencias, la cual demostró que el dispositivo puede operar en banda ancha resistiendo los efectos térmicos inherentes a cualquier amplificador de potencia.

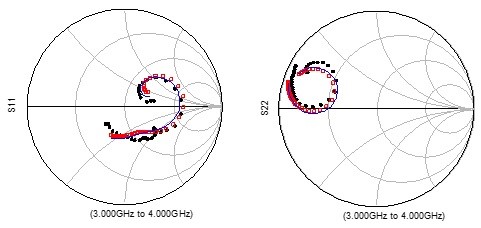

Se inició el análisis en condiciones de pequeña señal. Para ello, todos los elementos parásitos del dispositivo fueron medidos usando un analizador de redes y empleando el método indicado en [12]. Los modelos fueron implementados en ADS y validados en condiciones de pequeña señal y gran señal. Los resultados de parámetros S en estas condiciones se muestran en la Figura 4. Los puntos negros representan las medidas. Los cuadrados rojos indican la salida del modelo de ROOT, mientras que las líneas continuas sólidas de color azul simbolizan los resultados del modelo MET.

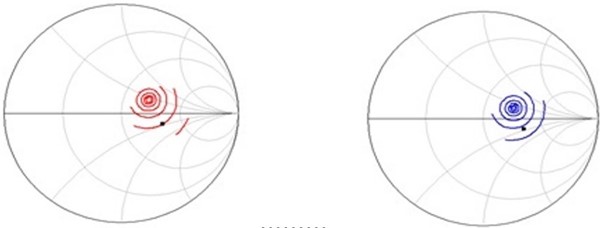

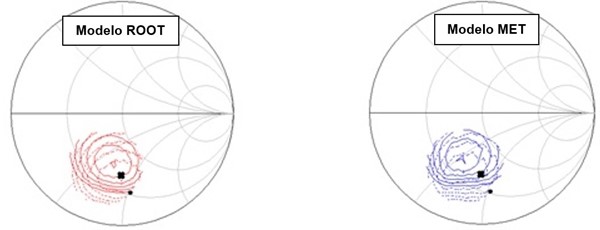

Ambos modelos fueron probados también bajo condiciones de Source-Pull. En esta prueba se midieron diferentes valores de impedancia de la fuente para obtener la mejor pérdida de retorno de entrada (IRL). Los resultados se muestran en la Figura 5. De este modo se lograron obtener los valores óptimos para las impedancias de fuente para los modelos mencionados anteriormente. Estos valores se comparan en la Figura 5 con el valor óptimo medido.

Fig. 5 Medida Source-Pull a 3.4GHzPuntos negros: impedancias óptimas medidas. Contornos rojos: modelo de ROOT. Contornos azules: modelo MET

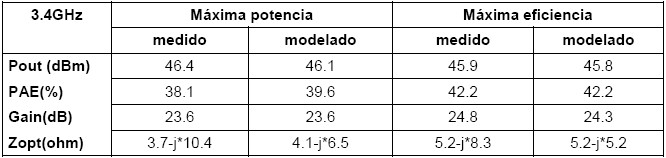

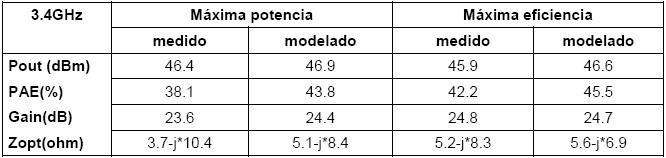

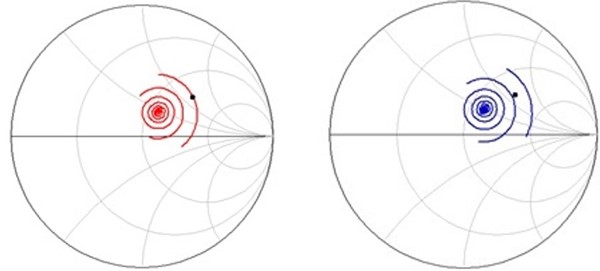

Con los valores óptimos de impedancia de fuente obtenidos anteriormente, se probó que los modelos en condiciones de Load-Pull para extraer el valor óptimo de la impedancia de carga, con el fin de obtener la potencia de salida máxima (Pout) y la eficiencia máxima (PAE). Como ya se señaló, la corriente de reposo se definió en 70 mA y 280mA, para la primera y segunda etapa respectivamente, para capturar adecuadamente el punto de compresión P1dB. En la Figura 6, los puntos representan las impedancias óptimas medidas, mientras que los contornos indican las simulaciones. Los valores máximos de potencia de salida y eficiencia obtenidos en el test anterior se muestran resumidos en formato numérico en las tablas 2 y 3 para ambos modelos. En estas tablas se pueden comparar las diferencias entre valores medidos y modelados.

Fig. 6 Medidas Load-Pull a 3.4GHz (Z0 = 10Ohms)Contornos de puntos: potencia de salida P1dB simulada. Puntos en negrita: impedancias óptimas P1dB medidas. Contornos sólidos: PAE simulado. Estrellas en negrita: impedancias óptimas del PAE medido

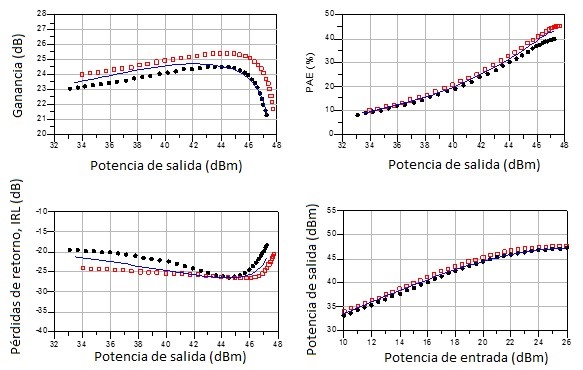

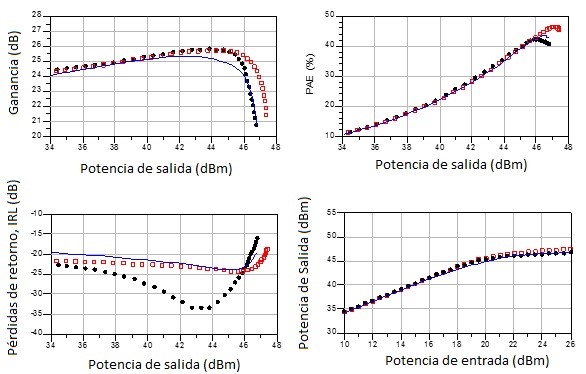

Para analizar el comportamiento global del RFIC se hicieron barridos de potencia a 3.4GHz para las condiciones de máxima potencia y máxima eficiencia. Los resultados se resumen en las figuras 7 y 8. Las curvas de medición se representan con puntos negros, las curvas de simulación ROOT están simbolizadas por cuadrados rojos, y las curvas de simulación MET, por líneas azules sólidas. La superioridad del modelo MET sobre ROOT es evidente en la mayoría de las figuras de mérito representadas. Esto se debe a la caracterización térmica precisa proporcionada por este modelo y a las capacidades mejoradas aportadas por la técnica de voltajes efectivos. En condiciones de compresión de ganancia de 1 dB, las diferencias entre las mediciones y la simulación son menores que 1 dB para la ganancia del modelo MET. En términos de PAE y potencia de salida, esta diferencia es inferior al 2 % y 1W respectivamente.

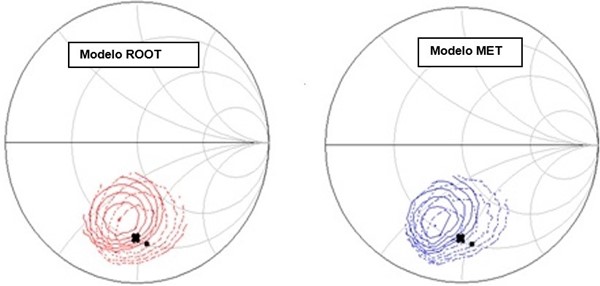

Fig. 9 Test de Source Pull a 3.6GHz: contornos de IRL simulados vs. el mejor valor medido de IRLLos puntos representan las impedancias óptimas medidas. Las curvas representan los contornos de IRL simulados tanto para el modelo de ROOT (rojo) como para el modelo MET (azul)

Fig. 10 Test de Load Pull a 3.6GHz. Zo=10 ohmsLos contornos punteados representan la potencia de salida P1dB simulada. Los puntos en negrita indican las impedancias óptimas medidas en condiciones de máximo P1dB. Los contornos sólidos representan el PAE simulado. Las cruces en negrita simbolizan las impedancias óptimas medidas en condiciones de máximo PAE

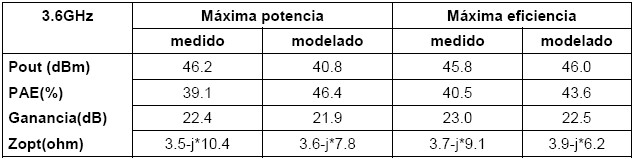

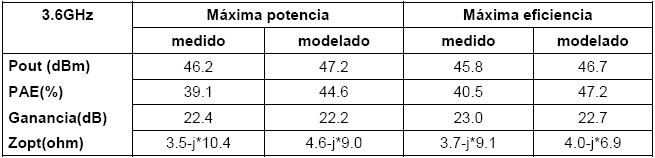

Las tablas 4 y 5 muestran la potencia, eficiencia y ganancia a 3.6 GHz. Comparando esos valores con los que se exponen en las tablas 2 y 3 se puede concluir que esos parámetros son casi constantes en 200 MHz. También se puede ver que el modelo MET brinda buenos resultados no solo a 3.4GHz, sino también a 3.6GHz.

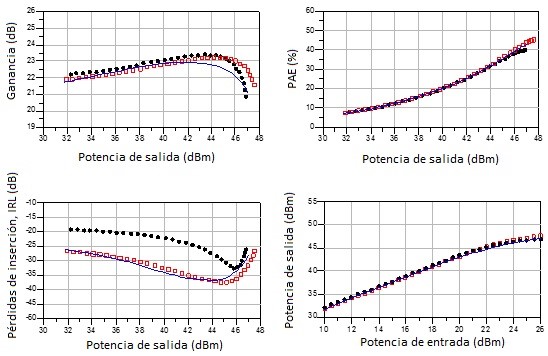

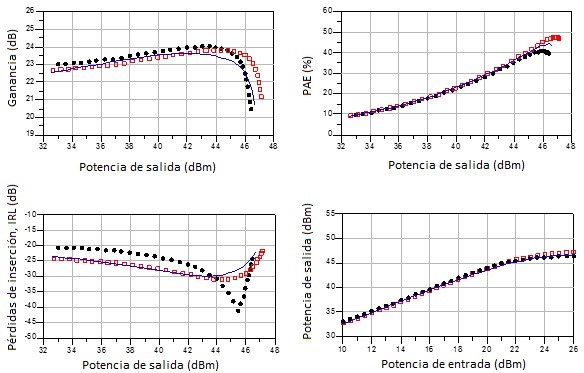

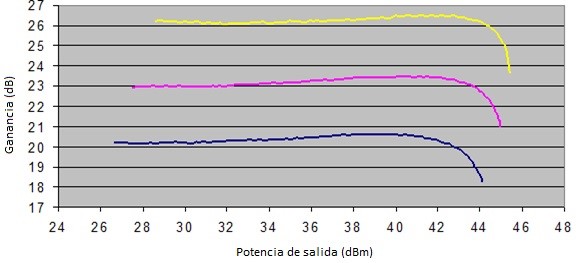

Para analizar el comportamiento global del dispositivo a 3.6GHz, se realizaron además medidas de barrido en potencia. Los resultados se resumen en las figuras 11 y 12 para la potencia de salida máxima y para el PAE máximo, respectivamente. Las curvas de medición están en puntos negros, las curvas de simulación ROOT están representadas por cuadrados rojos, y las curvas de simulación MET están en azul sólido. Se puede apreciar que, en este rango de alta frecuencia, el modelo MET también tiene más precisión que el modelo ROOT.

Tabla 4 Resultados del test Load-Pull en condiciones de 1dB de compresión de ganancia para el modelo MET a 3.6GHz

Tabla 5 Resultados del test Load-Pull en condiciones de 1dB de compresión de ganancia para el modelo ROOT a 3.6GHz

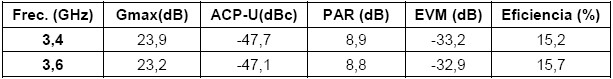

Usando herramientas de diseño CAD y con el método propuesto se logró construir un amplificador de potencia demostrativo en circuito impreso con n ancho de banda comprendido entre 3.4 y 3.6 GHz, el cual se detalla en [9]. Al polarizar el dispositivo en las condiciones adecuadas para evaluar el punto de compresión, y enviando una señal de entrada de un tono en onda continua, se obtuvo una ganancia superior a 22.8 dB, en condiciones de compresión 1dB, con una pequeña variación, cercana a 0.5 dB de 3.4 a 3.6 GHz, como se muestra en la Tabla 6. La respuesta del demoboard construido se midió también en condiciones Wimax. En [13], el RFIC se probó con una señal Wimax de 7 MHz. Para el presente trabajo se usó una señal de ancho de banda de 10 MHz con una modulación 64 QAM-3/4. La relación pico a promedio (PAR) fue de 9.5 dB a una probabilidad del 0.01 CCDF. Los resultados también se muestran en la Tabla 7. De esa tabla se puede ver además que considerando una potencia de salida de + 37 dBm de 3.4GHz a 3.6GHz, la eficiencia de las dos etapas es de aproximadamente el 15 % con una magnitud de vector de error (EVM) alrededor de -33 dB.

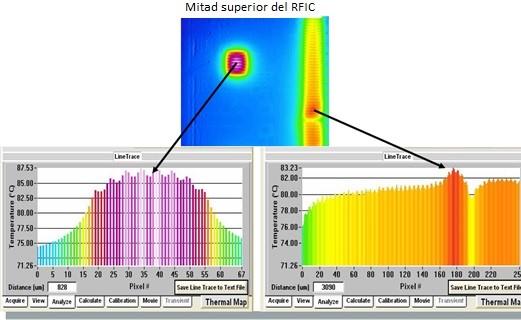

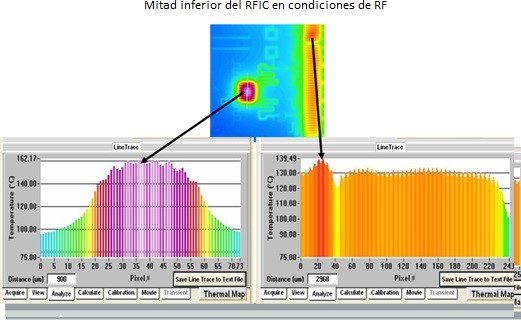

Una vez verificadas las funciones RF del demoboard implementado con la metodología propuesta, se hizo una verificación sobre el comportamiento del dispositivo con respecto al autocalentamiento. Para ello se comprobó la repetitividad de resultados haciendo unas pruebas de barrido hasta 3 dB de compresión de ganancia. Para esta prueba, denominada barrido P3dB, se midieron la potencia, la ganancia y la eficiencia. Por otro lado, la robustez del dispositivo también se verificó a través de mediciones de onda estacionaria (VSWR) utilizando línea de transmisión coaxial deslizante. Si bien es cierto que el amplificador no resultó dañado en estas pruebas, en este último test se observaron oscilaciones. Este problema se resolvió creando una red RC de estabilización cercana a las líneas de polarización de drenador. Esta red consiste de una resistencia de 10 ohmios en serie con un condensador de 33pF. Usando esta misma red de polarización, se repitieron las medidas anteriores y se obtuvieron los mismos resultados, garantizando la repetitividad del sistema. La ganancia también se midió con respecto a la temperatura, dando como resultado una variación de -0,05 dB / °C, lo que es normal para esta tecnología. Los resultados se muestran en la Figura 13: las líneas azul, rosada y amarilla representan las ganancias medidas a 90, 25 y -30 grados Celsius. La variación de la potencia de salida, expresada en Watts fue de -0.89W / °C. Esta variación pequeña es bastante buena y se debe a la técnica de seguimiento térmico (thermal tracking) [3]. Las mediciones de infrarrojos en la PCB con el transistor en condiciones de DC y sin aplicar señal de entrada (habiendo previamente extraído su encapsulado), mostraron 87 °C para el die y 83 °C para los hilos de salida (drain output wire bonds). En condiciones de RF, a 35W de potencia de salida, la temperatura de los hilos de salida fue de 180 °C. Esos resultados se muestran en las figuras 14 y 15.

Fig. 13 Medidas de ganancia y temperatura para test de un tono de onda continua a 3.6GHz haciendo un barrido en potencia

A partir de la prueba de infrarrojos se concluye que, en condiciones de DC, la distribución de la temperatura es casi constante para el RFIC. Para las condiciones de RF, la distribución de la temperatura es ligeramente más alta en el lado inferior. Para los cables de salida, la distribución de la temperatura en el lado inferior es casi 20 ° C más alta que en el lado superior. Sin embargo, tanto en DC como en RF se comprueba que las temperaturas máximas están por debajo de los máximos permisibles en un 20 %, lo cual garantiza la vida útil del amplificador [14] y demuestra la utilidad del modelo propuesto para predecir el comportamiento de este tipo de dispositivos.

IV. Discusión y conclusiones

En este artículo se presentó una técnica para mejorar el proceso industrial de diseño y fabricación de transistores de microondas. Se ha demostrado que la técnica DOE extendida y el modelo electrotérmico mejorado con la técnica de los voltajes efectivos han permitido la elaboración de un amplificador de potencia con los mejores valores posibles de potencia, eficiencia y linealidad. Se realizaron medidas de caracterización térmica que permitieron verificar que el dispositivo opera en su zona segura, lo cual garantiza la confiabilidad y la vida útil del sistema amplificador en su conjunto.

Como primer paso en la implementación de la técnica propuesta, se calcularon los efectos de las inductancias mutuas de los hilos de la red de preadaptación, los cuales fueron medidos por medio de un test de diseño de experimentos (DOE) extendido de siete variables. Al optimizar las alturas de los hilos, se consiguió centrar el diseño del circuito y obtener las dimensiones que generan el mejor desempeño. De este modo se evitó el uso de simulaciones electromagnéticas de acoplamiento mutuo inductivo, de alto costo computacional, ahorrando tiempo en el proceso de diseño.

Posteriormente se procedió a diseñar y construir un amplificador en circuito impreso, usando el dispositivo centrado anteriormente y se llegó a demostrar, a través de medidas de Load-Pull y de barrido en potencia, que con la modificación del modelo MET mediante la técnica de “voltajes efectivos” es posible obtener un amplificador de potencia de RF con valores óptimos de potencia, ganancia, eficiencia y linealidad.

Tal como lo demuestran las medidas y simulaciones, el modelo MET es más efectivo que el modelo convencional ROOT, pues está basado en un principio electrotérmico, el cual relaciona el efecto Joule que se crea en una resistencia con el calentamiento térmico que experimenta un transistor [4]. La resistencia se denomina resistencia térmica y está relacionada con la disipación del calor debida a la estructura del transistor. Para simular la constante de tiempo de la temperatura generada en el semiconductor, este modelo usa un capacitor denominado capacitor térmico, el cual modela la rapidez de disipación de calor al estar en paralelo con la resistencia antes mencionada. Esta combinación RC implementada con la técnica de voltajes efectivos [8], resulta efectiva para predecir los estados trampa en dispositivos de baja y alta potencia [5]. Para comprobar la eficiencia de este modelo electrotérmico extendido, se simularon las impedancias óptimas y también se llevaron a cabo mediciones con sistemas Load-Pull llegándose a obtener dichas impedancias con precisión. El demoboard elaborado a través de la síntesis de los valores de impedancia obtenidos anteriormente, fue probado en condiciones de pequeña señal y gran señal. Después de pasar la prueba P1dB, se llevaron a cabo mediciones en condición Wimax. La optimización fina en el banco se realizó para alcanzar el mejor compromiso entre ganancia, eficiencia y linealidad.

En último término se llevaron a cabo medidas de temperatura para verificar la robustez y estabilidad, y se llegó a la conclusión de que el amplificador trabaja dentro de la zona segura, sin exceder los límites de temperatura impuestos para esta tecnología, lo cual permite garantizar la vida útil del dispositivo.